Alam mo ba kung paano lutasin ang problema sa EMI kapag multi-layer na disenyo ng PCB?

Hayaan mo akong sabihin sa iyo!

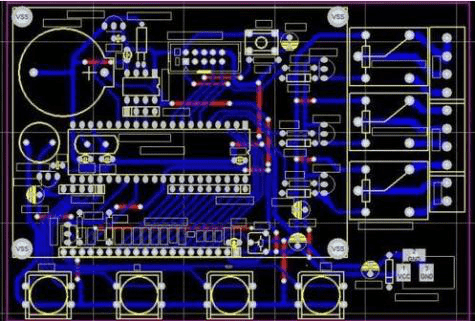

Mayroong maraming mga paraan upang malutas ang mga problema sa EMI.Kabilang sa mga modernong paraan ng pagsugpo sa EMI ang: paggamit ng EMI suppression coating, pagpili ng naaangkop na mga bahagi ng pagsugpo sa EMI at disenyo ng simulation ng EMI.Batay sa pinakapangunahing layout ng PCB, tinatalakay ng papel na ito ang function ng PCB stack sa pagkontrol sa EMI radiation at mga kasanayan sa disenyo ng PCB.

power bus

Ang output voltage jump ng IC ay maaaring mapabilis sa pamamagitan ng paglalagay ng naaangkop na capacitance malapit sa power pin ng IC.Gayunpaman, hindi ito ang katapusan ng problema.Dahil sa limitadong frequency response ng capacitor, imposible para sa capacitor na makabuo ng harmonic power na kailangan para malinis ang IC output sa buong frequency band.Bilang karagdagan, ang lumilipas na boltahe na nabuo sa power bus ay magdudulot ng pagbaba ng boltahe sa magkabilang dulo ng inductance ng decoupling path.Ang mga lumilipas na boltahe na ito ay ang pangunahing karaniwang mode na pinagmumulan ng interference ng EMI.Paano natin malulutas ang mga problemang ito?

Sa kaso ng IC sa aming circuit board, ang power layer sa paligid ng IC ay maaaring ituring na isang mahusay na high-frequency capacitor, na maaaring mangolekta ng enerhiya na na-leak ng discrete capacitor na nagbibigay ng high-frequency na enerhiya para sa malinis na output.Bilang karagdagan, ang inductance ng isang mahusay na layer ng kapangyarihan ay maliit, kaya ang lumilipas na signal na na-synthesize ng inductor ay maliit din, kaya binabawasan ang karaniwang mode na EMI.

Siyempre, ang koneksyon sa pagitan ng power supply layer at ang IC power supply pin ay dapat na maikli hangga't maaari, dahil ang tumataas na gilid ng digital signal ay mas mabilis at mas mabilis.Mas mainam na ikonekta ito nang direkta sa pad kung saan matatagpuan ang IC power pin, na kailangang talakayin nang hiwalay.

Upang makontrol ang karaniwang mode na EMI, ang power layer ay dapat na isang mahusay na idinisenyong pares ng mga power layer upang makatulong sa pag-decouple at magkaroon ng sapat na mababang inductance.Maaaring magtanong ang ilang tao, gaano ito kahusay?Ang sagot ay depende sa power layer, ang materyal sa pagitan ng mga layer, at ang operating frequency (ibig sabihin, isang function ng IC rise time).Sa pangkalahatan, ang spacing ng power layers ay 6mil, at ang interlayer ay FR4 material, kaya ang katumbas na capacitance per square inch ng power layer ay mga 75pF.Malinaw, mas maliit ang layer spacing, mas malaki ang capacitance.

Walang maraming mga aparato na may oras ng pagtaas ng 100-300ps, ngunit ayon sa kasalukuyang rate ng pag-unlad ng IC, ang mga aparato na may oras ng pagtaas sa hanay na 100-300ps ay sasakupin ang isang mataas na proporsyon.Para sa mga circuit na may 100 hanggang 300 PS na pagtaas ng beses, 3 mil na layer spacing ay hindi na naaangkop para sa karamihan ng mga application.Sa oras na iyon, kinakailangang gamitin ang teknolohiya ng delamination na may interlayer spacing na mas mababa sa 1mil, at palitan ang FR4 dielectric na materyal ng materyal na may mataas na dielectric constant.Ngayon, matutugunan ng mga ceramics at potted plastic ang mga kinakailangan sa disenyo ng 100 hanggang 300ps rise time circuit.

Bagama't ang mga bagong materyales at pamamaraan ay maaaring gamitin sa hinaharap, karaniwang 1 hanggang 3 ns rise time circuit, 3 hanggang 6 mil layer spacing, at FR4 dielectric na materyales ay kadalasang sapat upang mahawakan ang mga high-end na harmonic at gawing mababa ang mga lumilipas na signal, iyon ay. , ang karaniwang mode na EMI ay maaaring mabawasan nang napakababa.Sa papel na ito, ang halimbawa ng disenyo ng PCB layered stacking ay ibinigay, at ang layer spacing ay ipinapalagay na 3 hanggang 6 mil.

electromagnetic shielding

Mula sa punto ng view ng pagruruta ng signal, ang isang mahusay na diskarte sa layering ay dapat na ilagay ang lahat ng mga bakas ng signal sa isa o higit pang mga layer, na nasa tabi ng power layer o ground plane.Para sa power supply, ang isang mahusay na diskarte sa layering ay dapat na ang power layer ay katabi ng ground plane, at ang distansya sa pagitan ng power layer at ang ground plane ay dapat kasing maliit hangga't maaari, na tinatawag nating "layering" na diskarte.

PCB stack

Anong uri ng diskarte sa pagsasalansan ang makakatulong sa pagprotekta at pagsugpo sa EMI?Ipinapalagay ng sumusunod na layered stacking scheme na ang power supply current ay dumadaloy sa isang layer at ang solong boltahe o maramihang boltahe ay ipinamamahagi sa iba't ibang bahagi ng parehong layer.Ang kaso ng maraming mga layer ng kapangyarihan ay tatalakayin sa ibang pagkakataon.

4-ply na plato

Mayroong ilang mga potensyal na problema sa disenyo ng 4-ply laminates.Una sa lahat, kahit na ang layer ng signal ay nasa panlabas na layer at ang power at ground plane ay nasa panloob na layer, ang distansya sa pagitan ng power layer at ground plane ay masyadong malaki.

Kung ang kinakailangan sa gastos ay ang una, ang sumusunod na dalawang alternatibo sa tradisyonal na 4-ply board ay maaaring isaalang-alang.Pareho sa mga ito ay maaaring mapabuti ang pagganap ng pagsugpo ng EMI, ngunit ang mga ito ay angkop lamang para sa kaso kung saan ang density ng mga bahagi sa board ay sapat na mababa at may sapat na lugar sa paligid ng mga bahagi (upang ilagay ang kinakailangang copper coating para sa power supply).

Ang una ay ang ginustong pamamaraan.Ang mga panlabas na layer ng PCB ay lahat ng mga layer, at ang gitnang dalawang layer ay signal / power layer.Ang supply ng kuryente sa layer ng signal ay niruruta ng malalawak na linya, na ginagawang mababa ang impedance ng landas ng kasalukuyang supply ng kuryente at mababa ang impedance ng path ng signal microstrip.Mula sa pananaw ng kontrol ng EMI, ito ang pinakamahusay na 4-layer na istraktura ng PCB na magagamit.Sa pangalawang pamamaraan, ang panlabas na layer ay nagdadala ng kapangyarihan at lupa, at ang gitnang dalawang layer ay nagdadala ng signal.Kung ikukumpara sa tradisyonal na 4-layer board, ang pagpapabuti ng scheme na ito ay mas maliit, at ang interlayer impedance ay hindi kasing ganda ng tradisyonal na 4-layer board.

Kung ang wiring impedance ay dapat kontrolin, ang nasa itaas na stacking scheme ay dapat na maingat na ilagay ang mga kable sa ilalim ng tansong isla ng power supply at grounding.Bilang karagdagan, ang copper island sa power supply o stratum ay dapat na magkakaugnay hangga't maaari upang matiyak ang pagkakakonekta sa pagitan ng DC at mababang frequency.

6-ply na plato

Kung ang density ng mga bahagi sa 4-layer board ay malaki, ang 6-layer plate ay mas mahusay.Gayunpaman, ang shielding effect ng ilang stacking scheme sa disenyo ng 6-layer board ay hindi sapat, at ang transient signal ng power bus ay hindi nabawasan.Dalawang halimbawa ang tinalakay sa ibaba.

Sa unang kaso, ang power supply at lupa ay inilalagay sa pangalawa at ikalimang layer ayon sa pagkakabanggit.Dahil sa mataas na impedance ng copper clad power supply, napaka hindi kanais-nais na kontrolin ang karaniwang mode na EMI radiation.Gayunpaman, mula sa punto ng view ng signal impedance control, ang paraan na ito ay napaka tama.

Sa pangalawang halimbawa, ang power supply at ground ay inilalagay sa ikatlo at ikaapat na layer ayon sa pagkakabanggit.Ang disenyong ito ay malulutas ang problema ng tansong nakasuot ng impedance ng power supply.Dahil sa mahinang pagganap ng electromagnetic shielding ng layer 1 at layer 6, tumataas ang differential mode EMI.Kung ang bilang ng mga linya ng signal sa dalawang panlabas na layer ay pinakamaliit at ang haba ng mga linya ay napakaikli (mas mababa sa 1/20 ng pinakamataas na harmonic wavelength ng signal), ang disenyo ay maaaring malutas ang problema ng differential mode EMI.Ang mga resulta ay nagpapakita na ang pagsugpo sa differential mode EMI ay lalong mabuti kapag ang panlabas na layer ay napuno ng tanso at ang copper clad area ay grounded (bawat 1 / 20 wavelength interval).Tulad ng nabanggit sa itaas, ang tanso ay dapat ilagay

Oras ng post: Hul-29-2020